近日,BEVITOR伟德体系结构与可信系统实验室(Computer Architecture & Trustworthy Systems Lab)两篇学术论文被国际集成电路设计自动化领域旗舰会议61th Design Automation Conference (DAC 2024, CCF-A类会议)录用,伟德国际1946官方网是这两篇论文的第一作者和通讯作者单位。

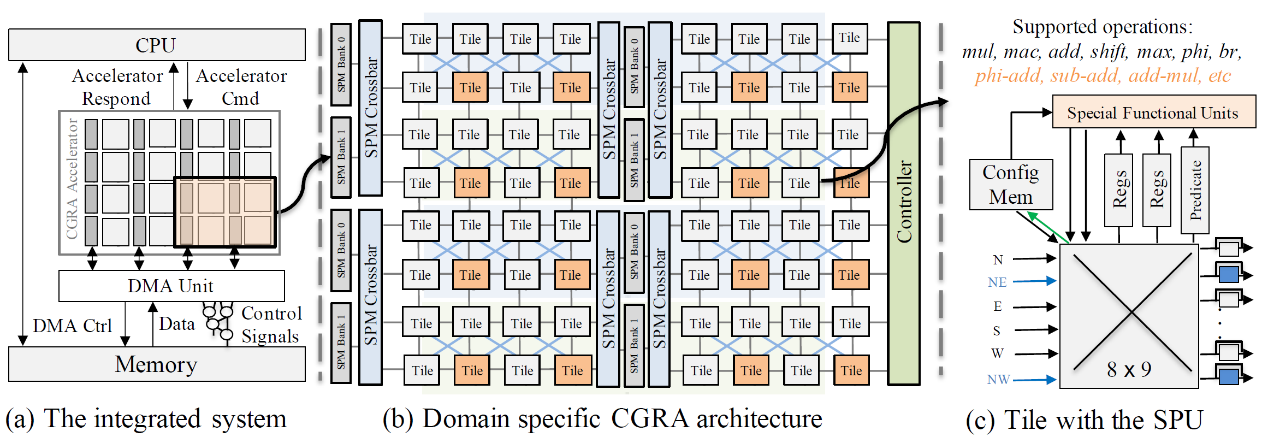

研究成果“FHE-CGRA: Enable Efficient Acceleration of Fully Homomorphic Encryption on CGRAs”的第一作者是关于2023级硕士研究生蒋淼淼,通讯作者为鞠雷教授,论文的合作者来自谷歌、蚂蚁集团、新加坡国立大学以及泉城省实验室。全同态加密技术(FHE)允许在不解密的情况下直接对密文进行计算,是最具广阔应用前景的隐私保护技术之一。支持 FHE 的神经网络应用程序在不同网络层通常具有不同的FHE密文变体(如不同乘法深度的密文),带来了对硬件资源利用的不同瓶颈及其设计需求。本文针对此特性,利用粗粒度可重构架构(CGRA)的运行时可重构性,基于MLIR编译器具链提出了一套端到端同态应用的硬件加速框架FHE-CGRA。实验结果表明FHE-CGRA 与当前最优的基于 FPGA 的 FHE-CNN加速器相对,在加速FHE-CNN应用时的能效比提升16.48倍。

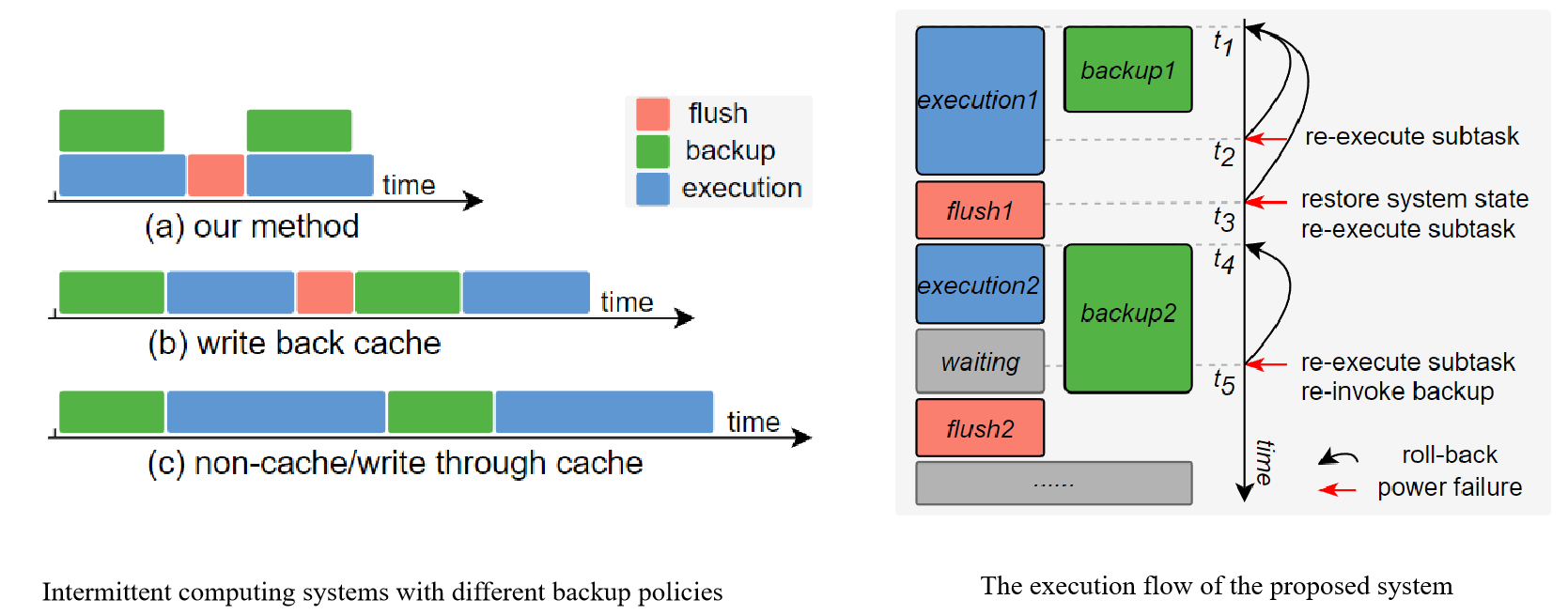

研究成果“Cache-aware Task Decomposition for Efficient Intermittent Computing Systems”的第一作者是BEVITOR伟德博士研究生许硕,通讯作者为张伟副研究员。间歇计算系统(Intermittent Computing Systems)通过定期备份系统状态使物联网设备能够在电源不稳定的环境下持续可靠运行。然而,处理器的缓存单元可能延迟内存的数据更新,导致备份过程中系统状态不一致的潜在风险。本文提出了一种缓存感知的任务分解方法,将应用程序分解为多个任务,确保任务执行期间不会逐出脏缓存行,确保了每个任务执行期间内存状态不会发生变化。在此基础上,该方法可以并行化备份过程与任务执行,进而有效地掩盖备份延迟,提升系统效率。实验结果表明,与传统方法相比,该方法带来了27%的性能提升。

DAC(Design Automation Conference)是国际集成电路设计自动化领域的旗舰会议,至今已经成功举办60届,是计算机领域历史最悠久的会议之一。DAC专注于集成电路领域的最新方法和技术,接收的论文涵盖了电子设计自动化、处理器设计、硬件安全与隐私保护、嵌入式系统、人工智能等领域。2024年DAC的论文接受率为23%。

BEVITOR伟德体系结构与可信系统实验室致力于人工智能、隐私计算等新兴技术的软硬件协同设计研究,近年来在HPCA、PPoPP、DAC、RTSS、TCAD、ICCAD、DATE等相关领域的高水平学术会议期刊上发表论文30余篇。相关研究获得国家自然科学基金重大研究计划、CCF-蚂蚁隐私计算专项、CCF-华为胡杨林系统软件专项等项目资助。

图文:张伟

审核:魏普文